——DWIN Froum-ek partekatua

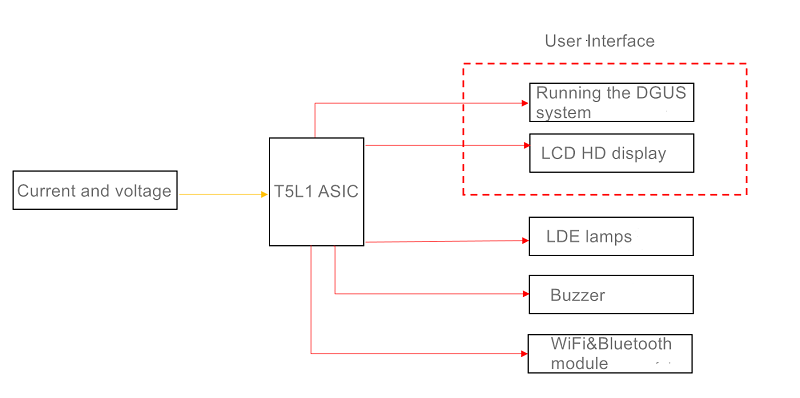

DWIN T5L1 txipa makina osoaren kontrol-nukleo gisa erabiliz, ukimena, ADC eskuratzea, PWM kontrolaren informazioa jasotzen eta prozesatzen du eta 3,5 hazbeteko LCD pantaila gidatzen du uneko egoera denbora errealean bistaratzeko.Onartu LED argi iturriaren distira urruneko ukipenaren doikuntza WiFi moduluaren bidez eta ahots-alarma onartzen.

Programaren ezaugarriak:

1. Hartu T5L txipa maiztasun altuan exekutatzeko, AD laginketa analogikoa egonkorra da eta errorea txikia da;

2. Onartu C MOTA zuzenean ordenagailura konektatuta arazketa eta programak grabatzeko;

3. Abiadura handiko OS core interfazea onartzen du, 16 biteko ataka paraleloa;UI core PWM ataka, AD ataka irteera, kostu baxuko aplikazioen diseinua, ez da MCU gehigarririk gehitu beharrik;

4. WiFi, Bluetooth urruneko kontrola onartzen;

5. Onartu 5 ~ 12V DC tentsio zabala eta sorta zabaleko sarrera

1.1 Eskema-diagrama

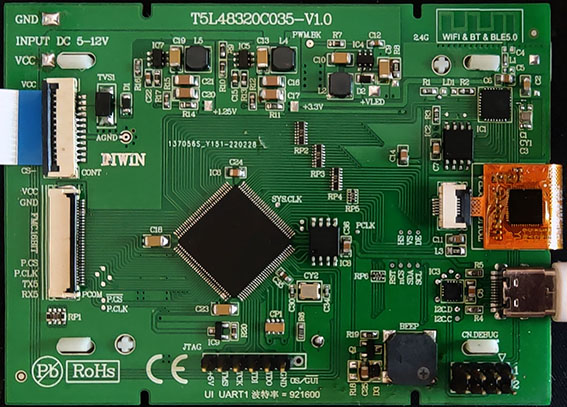

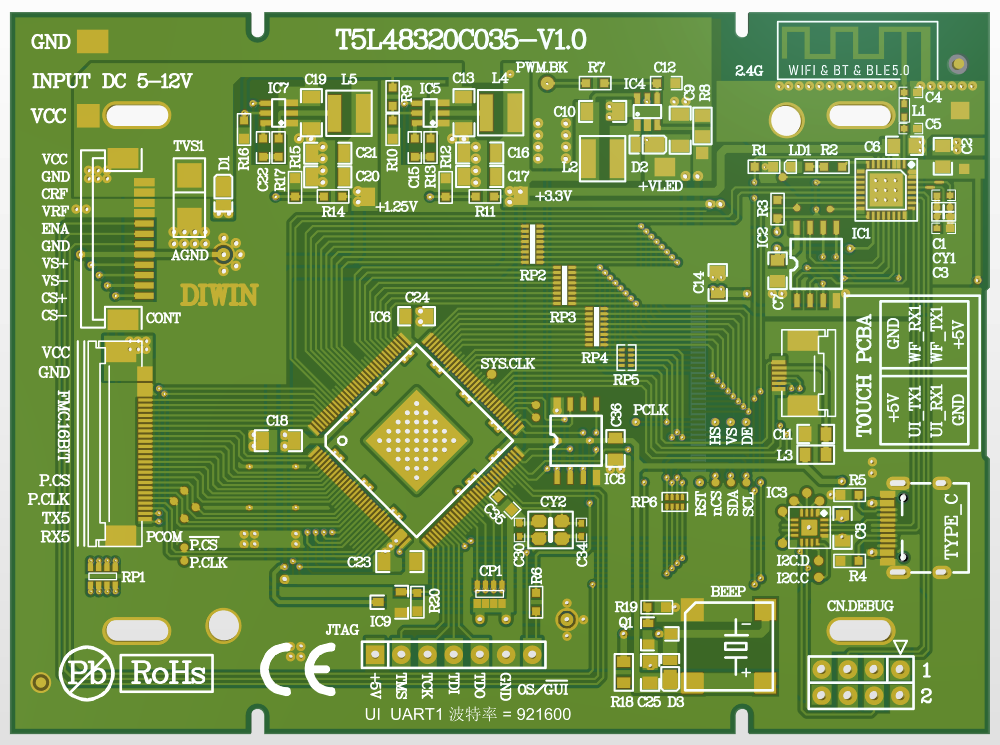

1.2 PCB plaka

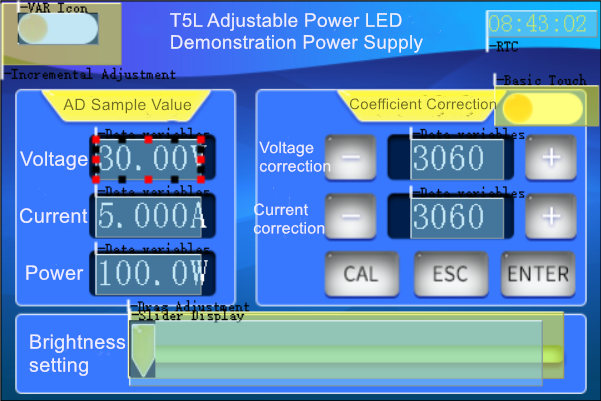

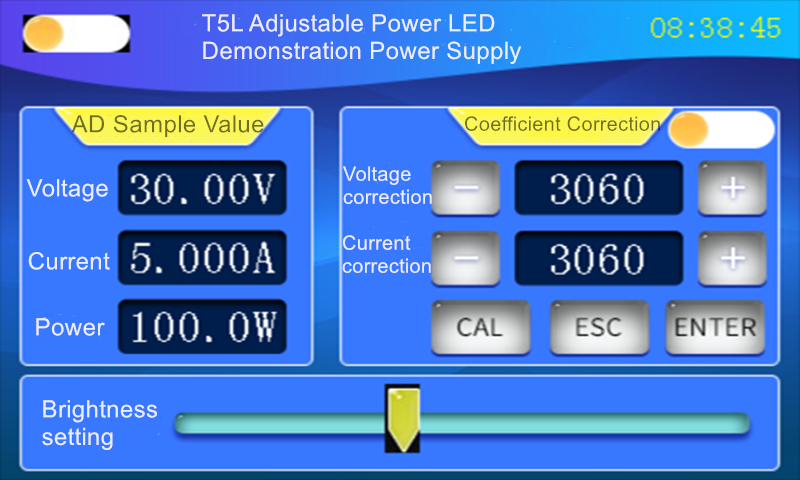

1.3 Erabiltzaile-interfazea

Lotsa sarrera:

(1)Hardware-zirkuitu diseinua

1.4 T5L48320C035 zirkuitu-eskema

1. MCU elikadura logikoa 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU core elikadura hornidura 1.25V: C23, C24;

3. MCU hornidura analogikoa 3.3V: C35 MCUrako hornidura analogikoa da.Tipografia egiterakoan, nukleoa 1.25V lurra eta lurra logikoa elkarrekin konbina daitezke, baina lur analogikoa bereizi behar da.Lur analogikoa eta lur digitala LDO irteerako kondentsadore handiaren polo negatiboan bildu behar dira, eta polo positibo analogikoa LDO kondentsadore handiaren polo positiboan ere bildu behar da, AD laginketa Zarata minimizatzeko.

4. AD seinale analogikoa eskuratzeko zirkuitua: CP1 AD sarrera analogikoko iragazki-kondentsadorea da.Laginketa-errorea murrizteko, MCUaren lur analogikoa eta lur digitala modu independentean bereizten dira.CP1-ren polo negatiboa MCUaren lur analogikora konektatu behar da inpedantzia minimoarekin, eta kristal osziladorearen bi kondentsadore paraleloak MCUaren lur analogikora konektatuta daude.

5. Buzzer-zirkuitua: C25 burrunbagailuaren elikadura-kondentsadorea da.Burrunbagailua indukziozko gailu bat da, eta funtzionamenduan zehar korronte gailurra egongo da.Gailurra murrizteko, beharrezkoa da burrunbagailuaren MOS disko-korrontea murriztea MOS hodiak eskualde linealean funtziona dezan, eta zirkuitua diseinatzea etengailu moduan funtziona dezan.Kontuan izan R18 burrunbagailuaren bi muturretan paraleloan konektatu behar dela burrunbagailuaren soinu-kalitatea doitzeko eta burrunbagailuaren soinua kurruskaria eta atsegina izan dadin.

6. WiFi zirkuitua: WiFi txiparen laginketa ESP32-C, WiFi+Bluetooth+BLErekin.Kablean, RF potentzia-lurra eta seinale-lurra bereizten dira.

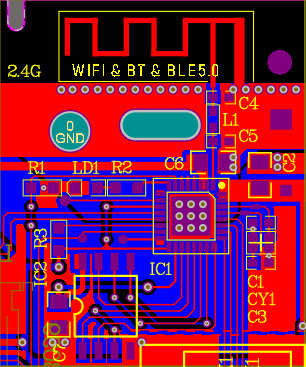

1.5 WiFi zirkuituaren diseinua

Goiko irudian, kobrezko estalduraren goiko aldea potentzia-lurraren begizta da.WiFi antena isladatzeko lurraren begiztak eremu handi bat izan behar du potentzia-lurraren aldera, eta potentzia-lurraren bilketa-puntua C6-ren polo negatiboa da.Korronte isladatua eman behar da elektrizitate-lurraren eta WiFi antenaren artean, beraz, WiFi antenaren azpian kobrezko estaldura egon behar da.Kobrezko estalduraren luzerak WiFi antenaren luzapenaren luzera gainditzen du, eta luzapenak WiFiaren sentsibilitatea handituko du;puntu C2-ren polo negatiboan.Kobre-eremu handi batek WiFi antena-erradiazioak eragindako zarata babestu dezake.Kobrezko 2 zoruak beheko geruzan bereizten dira eta ESP32-C-ren erdiko kutxan biltzen dira bideen bidez.RF potentzia-lurrak seinale-lurraren begizta baino inpedantzia txikiagoa behar du, beraz, 6 bide daude potentzia-lurretik txip padraino inpedantzia nahiko baxua ziurtatzeko.Kristal-osziladorearen lurreko begiztak ezin du RF potentziarik izan bertatik igarotzen, bestela kristal-osziladoreak maiztasun-jitter sortuko du, eta WiFi maiztasunaren desplazamenduak ezin izango ditu datuak bidali eta jaso.

7. Atzeko argia LED elikadura-zirkuitua: SOT23-6LED kontrolatzailearen txiparen laginketa.LEDaren DC/DC elikadura-hornidurak modu independentean begizta bat osatzen du, eta DC/DC lurra 3.3V LOD lurrera konektatuta dago.PWM2 ataka nukleoa espezializatua denez, 600K PWM seinalea ateratzen du eta RC bat gehitzen da PWM irteera ON/OFF kontrol gisa erabiltzeko.

8. Tentsioaren sarrera-barrutia: DC/DC bi jaitsiera diseinatzen dira.Kontuan izan DC/DC zirkuituko R13 eta R17 erresistentziak ezin direla baztertu.Bi DC/DC txipek 18V-ko sarrerara onartzen dute, kanpoko elikadurarako erosoa dena.

9. USB MOTA C arazketa ataka: C MOTA aurrera eta atzera konektatu eta deskonektatu daiteke.Aurrera sartzea WIFI txiparekin komunikatzen da ESP32-C WIFI txipa programatzeko;alderantzizko txertaketa XR21V1410IL16-rekin komunikatzen da T5L programatzeko.C MOTA 5V-ko elikadura-hornidura onartzen du.

10. Portu paraleloen komunikazioa: T5L OS coreak doako IO portu asko ditu, eta 16 biteko ataka paraleloko komunikazioa diseinatu daiteke.ST ARM FMC ataka paraleloen protokoloarekin konbinatuta, irakurketa eta idazketa sinkronoa onartzen du.

11. LCM RGB abiadura handiko interfazearen diseinua: T5L RGB irteera zuzenean LCM RGB-ra konektatzen da, eta buffer erresistentzia erdian gehitzen da LCM uraren uhinen interferentzia murrizteko.Kableatzerakoan, murriztu RGB interfazearen konexioaren luzera, batez ere PCLK seinalea, eta handitu RGB interfazea PCLK, HS, VS, DE proba-puntuak;pantailaren SPI ataka T5L-ren P2.4 ~ P2.7 portuetara konektatuta dago, eta hori erosoa da pantaila kontrolatzailea diseinatzeko.Eraman RST, nCS, SDA, SCI proba-puntuak azpiko softwarearen garapena errazteko.

(2) DGUS interfazea

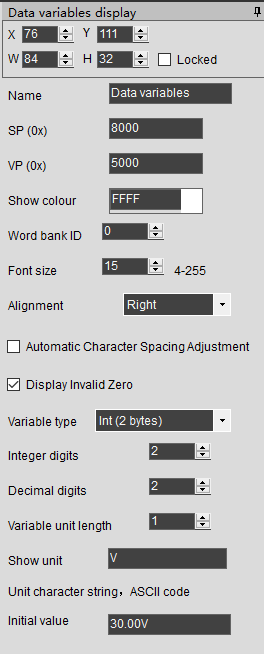

1.6 Datu aldagaien bistaratzeko kontrola

(3) OS

//———————————DGUS irakurtzeko eta idazteko formatua

typedef egitura

{

u16 adr;//UI 16 biteko aldagaiaren helbidea

u8 datLen;//8bitdatuen luzera

u8 *pBuf;//8 biteko datu erakuslea

} UI_packTypeDef;//DGUS irakurri eta idatzi paketeak

//——————————-datuen aldagaien bistaratzeko kontrola

typedef egitura

{

u16 LH;

u16 X;

u16 Y;

u16 Kolorea;

u8 Lib_ID;

u8 FontSize;

u8 Lerrokatzea;

u8 IntNum;

u8 DecNum;

u8 Mota;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;//datuen aldagaien deskribapen egitura

typedef egitura

{

Number_spTypeDef sp;//SP deskribapen erakuslea definitu

UI_packTypeDef spPack;// Definitu SP aldagaia DGUS irakurri eta idatzi paketea

UI_packTypeDef vpPack;//definitu vp aldagaia DGUS irakurri eta idatzi paketea

} Number_HandleTypeDef;//datuen aldagaien egitura

Aurreko datu aldagaiaren heldulekuaren definizioarekin.Ondoren, definitu aldagai bat tentsio-laginketaren pantailarako:

Number_HandleTypeDef Hsample;

u16 tentsio_lagina;

Lehenik eta behin, exekutatu hasierako funtzioa

NumberSP_Init(&Hlagina,tentsio_lagina,0×8000);//0×8000 hona hemen deskribapen erakuslea

//——SP erakuslearen egituraren hasierako hasiera erakusten duen datu-aldagaia——

void NumberSP_Init(Number_HandleTypeDef *zenbakia,u8 *balioa, u16 zenbakiaAddr)

{

zenbakia->spPack.addr = zenbakiaAddr;

zenbakia->spPack.datLen = sizeof(zenbakia->sp);

zenbakia->spPack.pBuf = (u8 *)&zenbakia->sp;

Irakurri_Dgus(&zenbakia->spPack);

zenbakia->vpPack.addr = zenbakia->sp.VP;

switch(zenbakia->sp.Type) //Vp aldagaiaren datu-luzera automatikoki hautatzen da DGUS interfazean diseinatutako datu-aldagai motaren arabera.

{

0 kasua:

5. kasua:

zenbakia->vpPack.datLen = 2;

hautsi;

1. kasua:

2. kasua:

3. kasua:

6. kasua:

zenbakia->vpPack.datLen = 4;

4. kasua:

zenbakia->vpPack.datLen = 8;

hautsi;

}

zenbakia->vpPack.pBuf = balioa;

}

Hasieratu ondoren, Hsample.sp tentsio-laginketaren datu-aldagaiaren deskribapen erakuslea da;Hsample.spPack sistema eragilearen nukleoaren eta UI tentsioaren laginketa datuen aldagaiaren arteko komunikazio erakuslea da DGUS interfazearen funtzioaren bidez;Hsample.vpPack tentsio-laginketaren datu-aldagaia aldatzeko atributua da, adibidez, letra-tipoen koloreak, etab. IU-ren nukleora ere pasatzen dira DGUS interfazearen funtzioaren bidez.Hsample.vpPack.addr tentsioaren laginketa-datuen aldagaiaren helbidea da, hasierako funtziotik automatikoki lortu dena.DGUS interfazean helbide aldagaia edo datu aldagai mota aldatzen duzunean, ez dago zertan aldagaiaren helbidea OSaren nukleoan modu sinkronoan eguneratu.OS nukleoak voltage_sample aldagaia kalkulatu ondoren, Write_Dgus(&Hsample.vpPack) funtzioa exekutatu behar du eguneratzeko.Ez dago DGUS transmisiorako tentsio_lagina ontziratu beharrik.

Argitalpenaren ordua: 2022-06-15